February 26, 2018

NEW LIMITS center to enhance computer chip parts for upcoming advancements

WEST LAFAYETTE, Ind. — Purdue University is leading a new center to overcome the challenges of critical parts needed for low-power, high-performance computer chips in consumer electronics, vehicles and national security.

The NEW LIMITS center is a three-year project supported by $4.5 million from a collaboration between the Semiconductor Research Corp. (SRC) and the National Institute of Standards and Technology (NIST). NEW LIMITS will be one of four centers in the SRC nanoelectronics Computing Research (nCORE) program, and the only center selected to receive NIST funding. The SRC consortium operates university research programs both in the U.S. and globally, connecting them with sponsors in the semiconductor research industry. NIST, a non-regulatory agency of the U.S. Department of Commerce, advances measurement science, standards and technology to promote U.S. innovation and competitiveness. Purdue is working on the project with researchers from Pennsylvania State University, the University of Michigan, the University of Texas at Dallas and Stanford University.

Established in January, NEW LIMITS is named for three aspects of a computer chip that the center’s researchers aim to improve: NEW materials for LogIc, Memory and InTerconnectS.

“We won’t be able to deliver a new chip to the industry, but we will provide viable solutions for these three major components,” said Zhihong Chen, Purdue professor of electrical and computer engineering (ECE), who will be directing NEW LIMITS. Other Purdue faculty involved in the center are Joerg Appenzeller, the Barry M. and Patricia L. Epstein Professor of ECE, and assistant ECE professor Sumeet Gupta.

As devices such as smartphones get thinner and more advanced, the chips that enable their “smart” characteristics need to adapt. Industries have so far downsized the basic components of computer chips so much that they struggle to provide the desired performance at low power that new technologies need. Major corporations rely upon university research centers to investigate ways to prepare chips for increasingly more complex uses.

“There comes a point when conventional chip components can’t be scaled down any further,” Chen said.

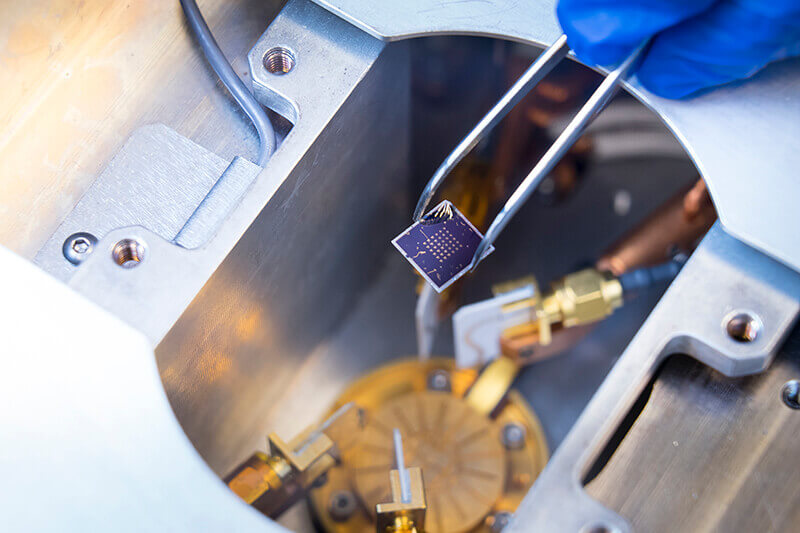

To make computers faster with less power, Purdue researchers will develop new materials for enhancing a chip’s logic, memory and interconnects. (Purdue University photo/Vincent Walter)

Download image

To make computers faster with less power, Purdue researchers will develop new materials for enhancing a chip’s logic, memory and interconnects. (Purdue University photo/Vincent Walter)

Download image

A computer chip is made up of silicon complementary metal-oxide-semiconductor (CMOS) transistors, which switch electrical signals, and copper interconnects that transfer those signals between transistors. Technological advancements have required smaller transistors that tend to overheat and more compact interconnects that do not pass currents as efficiently. The copper of interconnects also tends to diffuse into other areas of the chip and short out the transistors they are trying to connect.

The redesign of interconnects is a priority for the center. “If the copper shorts out at the wrong spots, then the entire chip can fail,” Chen said.

Chen and other researchers believe that using ultra-thin 2-D materials with a thickness of merely a couple of atoms, as opposed to bulkier 3-D materials, enhance silicon transistor and copper interconnect performance while also maintaining a smaller size. “Logic” in this sense would refer to blanketing silicon and copper with a single layer of atoms to double or triple the current drive.

This method would be more reasonable than replacing silicon in particular, Chen said, as 20 years of research still has not found a comparable replacement. “We actually do not need to replace it,” she said. “We would instead largely enhance the performance of current technology.”

As the center addresses interconnect and logic aspects of a chip’s performance, the researchers will also consolidate data storage and retrieval into a new type of memory cell. This would make computing and storage more efficient in a chip, and then for the computer as a whole.

“Collaboration with notable partners like SRC, NIST and the leading research institutions involved on this project are crucial to realizing the transformational scientific breakthroughs that will power the future of electronics,” said Suresh Garimella, Purdue's executive vice president for research and partnerships and the R. Eugene and Susie E. Goodson Distinguished Professor of Mechanical Engineering.

Chen, Appenzeller and a University of Michigan professor will specifically design and fabricate logic and memory devices and interconnects. The center combines expertise in 3-D materials and faculty from other universities who will investigate and manufacture the 2-D materials needed for each of these chip components. Gupta will design circuits with logic in memory functionalities and help with a benchmarking device and circuit performance for the semiconductor industry’s needs.

“SRC’s nanoelectronic computing research program offers important support to this exciting area,” said Mung Chiang, Purdue’s John A. Edwardson Dean of the College of Engineering. “As the name suggests, this center will develop new materials with unique electronic properties and push the limit of computing.”

Researchers have no choice but to push the limit of CMOS technology at this stage, Chen said. “Everything is counting on that chip’s performance.”

Information about the SRC can be found at https://www.src.org/, and the NIST at https://www.nist.gov.

Writer: Kayla Wiles, 765-494-2432, wiles5@purdue.edu

Source: Zhihong Chen, 765-494-0772, zhchen@purdue.edu